MC146818A

## **Advance Information**

3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721

#### REAL-TIME CLOCK PLUS RAM (RTC)

The MC146818A Real-Time Clock plus RAM is a peripheral device which includes the unique MOTEL concept for use with various microprocessors, microcomputers, and larger computers. This part combines three unique features: a complete time-of-day clock with alarm and one hundred year calendar, a programmable periodic interrupt and square-wave generator, and 50 bytes of low-power static RAM. The MC146818A uses high-speed CMOS technology to interface with 1 MHz processor buses, while consuming very little power.

The Real-Time Clock plus RAM has two distinct uses. First, it is designed as a battery powered CMOS part (in an otherwise NMOS/TTL system) including all the common battery backed-up functions such as RAM, time, and calendar. Secondly, the MC146818A may be used with a CMOS microprocessor to relieve the software of the timekeeping workload and to extend the available RAM of an MPU such as the MC146805E2.

- Low-Power, High-Speed CMOS

- Internal Time Base and Oscillator

- Counts Seconds, Minutes, and Hours of the Day

- Counts Days of the Week, Date, Month, and Year

- 3 V to 6 V Operation

- Time Base Input Options: 4.194304 MHz, 1.048576 MHz, or 32.768 kHz

- Time Base Oscillator for Parallel Resonant Crystals

- 40 to 200 μW Typical Operating Power at Low Frequency Time Base

- 4.0 to 20 mW Typical Operating Power at High Frequency Time Base

- Binary or BCD Representation of Time, Calendar, and Alarm

- 12- or 24-Hour Clock with AM and PM in 12-Hour Mode

- Daylight Savings Time Option

- Automatic End of Month Recognition

- Automatic Leap Year Compensation

- Microprocessor Bus Compatible

- Selectable Between Motorola and Competitor Bus Timing

- Multiplexed Bus for Pin Efficiency

- Interfaced with Software as 64 RAM Locations

- 14 Bytes of Clock and Control Registers

- 50 Bytes of General Purpose RAM

- Status Bit indicates Data Integrity

- Bus Compatible Interrupt Signals (IRQ)

- Programmable Square-Wave Output Signal

- Clock Output May Be Used as Microprocessor Clock Input At Time Base Frequency + 1 or +4

- 24-Pin Dual-In-Line Package

- Quad Pack Also Available

## **CMOS**

(HIGH-PERFORMANCE SILICON-GATE COMPLEMENTARY MOS)

> REAL-TIME CLOCK PLUS RAM

#### PIN ASSIGNMENT MOT [ 24**0** V<sub>DD</sub> OSC1 Q2 23**1** SQW 22**1** PS OSC2 d3 21 CKOUT AD0 14 20 CKFS AD1 15 19 1 IRQ AD2 16 18 RESET AD3 🛛 7 17 DS AD4 **[**8 AD5 19 16 STBY 15 1 R/W AD6 110 AD7 🗖11 14 🛮 AS 13 🗖 CS VSS 📮 12

## MAXIMUM RATINGS (Voltages referenced to VSS)

| Ratings                                                | Symbol           | Value                                                     | Unit |

|--------------------------------------------------------|------------------|-----------------------------------------------------------|------|

| Supply Voltage                                         | V <sub>DD</sub>  | -0.3 to +8.0                                              | V    |

| All Input Voltages Except OSC1                         | V <sub>in</sub>  | $V_{SS} - 0.5$ to $V_{DD} + 0.5$                          | ٧    |

| Current Drain per Pin Excluding VDB and VSS            | 1                | 10                                                        | mA   |

| Operating Temperature Range<br>MC146818A<br>MC146818AC | TA               | T <sub>L</sub> to T <sub>H</sub><br>0 to 70<br>– 40 to 85 | °C   |

| Storage Temperature Range                              | T <sub>stg</sub> | -55 to +150                                               | °C   |

#### THERMAL CHARACTERISTICS

| Characteristic     | Symbol           | Value | Unit |

|--------------------|------------------|-------|------|

| Thermal Resistance |                  |       |      |

| Plastic            |                  | 120   | ĺ    |

| Cerdip             | $\theta_{ m JA}$ | 65    | °C/W |

| Ceramic            | 97.              | 50    | Ì    |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ).

DC ELECTRICAL CHARACTERISTICS (V<sub>DD</sub>=3 Vdc, V<sub>SS</sub>=0 Vdc, T<sub>A</sub>=T<sub>L</sub> to T<sub>H</sub> unless otherwise noted)

|                                                                                                                 | Characteristics                                                 | Symbol           | Min                                | Max                                                   | Unit |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------|------------------------------------|-------------------------------------------------------|------|

| Frequency of Operation                                                                                          |                                                                 | fosc             | 32.768                             | 32.768                                                | kHz  |

| Output Voltage                                                                                                  |                                                                 | VOL              | _                                  | 0.1                                                   | V    |

| $L_{oad}$ < 10 $\mu$ A                                                                                          |                                                                 | Voн              | V <sub>DD</sub> - 0.1              | _                                                     | V    |

| $I_{DD}$ — Bus Idle<br>CKOUT = $f_{OSC}$ , $C_L = 1$<br>$f_{OSC} = 32.768 \text{ kHz}$                          | 5 pF; SQW Disabled, STBY = 0.2 V; C <sub>L</sub> (OSC2) = 10 pF | DD3              | _                                  | 50                                                    | μΑ   |

| I <sub>DD</sub> — Quiescent<br>f <sub>OSC</sub> = DC; OSC1= DC<br>All Other Inputs= V <sub>DE</sub><br>No Clock |                                                                 | I <sub>DD4</sub> | <b>-</b> .                         | 50                                                    | μΑ   |

| Output High Voltage (ILoad = -0.25 mA, A                                                                        | All Outputs)                                                    | Voн              | 2.7                                |                                                       | V    |

| Output Low Voltage<br>(I <sub>Load</sub> =0.25 mA, All                                                          | Outputs)                                                        | VOL              | ~                                  | 0.3                                                   | ٧    |

| Input High Voltage                                                                                              | STBY, AD0-AD7, DS, AS, R/W, CS<br>RESET, CKFS, PS, OSC1<br>MOT  | ViH              | 2.1<br>2.5<br>VDD                  | V <sub>DD</sub><br>V <sub>DD</sub><br>V <sub>DD</sub> | V    |

| Input Low Voltage                                                                                               | STBY, ADO-AD7, DS, AS, R/W, CS, CKFS, PS, RESET, OSC1<br>MOT    | VIL              | V <sub>SS</sub><br>V <sub>SS</sub> | 0.5<br>V <sub>SS</sub>                                | V    |

| Input Current                                                                                                   | AS, DS, R/W<br>MOT, OSCI, CE, STBY, RESET, CKFS, PS             |                  | _                                  | ± 10<br>± 1                                           | μΑ   |

| Three-State Leakage                                                                                             | ĪRQ, ADQ-AD7                                                    | İTSL             | _                                  | ± 10                                                  | μΑ   |

DC ELECTRICAL CHARACTERISTICS (VDD = 5 Vdc ±10%, VSS = 0 Vdc, TA = TL to TH unless otherwise noted)

| Characteristics                                                                                                                               | Symbol           | Min                   | Max             | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----------------|------|

| Frequency of Operation                                                                                                                        | fosc             | 32.768                | 4194.304        | kHz  |

| Output Voltage                                                                                                                                | Vol              | _                     | 0.1             |      |

| _ I <sub>Load</sub> <10 μA                                                                                                                    | VOH              | V <sub>DD</sub> -0.1  | _               | V    |

| IDD — Bus Idle (External Clock)  CKOUT = f <sub>OSC</sub> , C <sub>I</sub> = 15 pF; SQW Disabled, STBY = 0.2 V; C <sub>I</sub> (OSC2) = 10 pF |                  |                       |                 |      |

| f <sub>osc</sub> =4.194304 MHz                                                                                                                | IDD1             | _                     | 3               | mA   |

| f <sub>osc</sub> =1.048516 MHz                                                                                                                | IDD2             | _                     | 800             | μΑ   |

| f <sub>OSC</sub> =32.768 kHz                                                                                                                  | IDD3             |                       | 50              | μΑ   |

| I <sub>DD</sub> — Quiescent                                                                                                                   | I <sub>DD4</sub> | _                     | 50              | μΑ   |

| $f_{OSC} = DC$ ; OSC1 = DC;                                                                                                                   |                  |                       |                 |      |

| All Other Inputs=V <sub>DD</sub> -0.2 V;                                                                                                      |                  |                       |                 |      |

| No Clock                                                                                                                                      |                  |                       |                 |      |

| Output High Voltage                                                                                                                           |                  |                       |                 |      |

| (I <sub>Load</sub> = -1.6 mA, AD0-AD7, CKOUT)                                                                                                 | ∨он              | 4.1                   | _               | V    |

| (I <sub>Load</sub> = -1.0 mA, SQW)                                                                                                            |                  |                       |                 |      |

| Output Low Voltage                                                                                                                            |                  |                       |                 |      |

| (I <sub>Load</sub> = 1.6 mA, ADO-AD7, CKOUT)                                                                                                  | VOL              | _                     | 0.4             | V    |

| (I <sub>Load</sub> = 1.0 mA, IRQ and SQW)                                                                                                     |                  |                       |                 |      |

| Input High Voltage STBY, CFKS, AD0-AD7, DS, AS, R/W, CS, PS                                                                                   |                  | V <sub>DD</sub> – 2.0 | $v_{DD}$        |      |

| RESET                                                                                                                                         | ViH              | V <sub>DD</sub> = 0.8 | $V_{DD}$        | V    |

| OSC1                                                                                                                                          | }                | V <sub>DD</sub> – 1.0 | $V_{DD}$        |      |

| MOT                                                                                                                                           |                  | $V_{DD}$              | V <sub>DD</sub> |      |

| Input Low Voltage CKFS, PS, RESET, STBY, AD0-AD7, DS, AS, R/W, CS, OSC1                                                                       | VIL              | VSS                   | 0.8             | ٧    |

| MOT                                                                                                                                           |                  | V <sub>SS</sub> _     | VSS             |      |

| Input Current AS, DS, R/W                                                                                                                     | l <sub>in</sub>  |                       | ± 10            | μΑ   |

| MOT, OSCI, CE, STBY, RESET, CKFS, PS                                                                                                          |                  | _                     | ±1              | ,    |

| Three-State Leakage IRQ, AD0-AD7                                                                                                              | ITSL             | -                     | ± 10            | μA   |

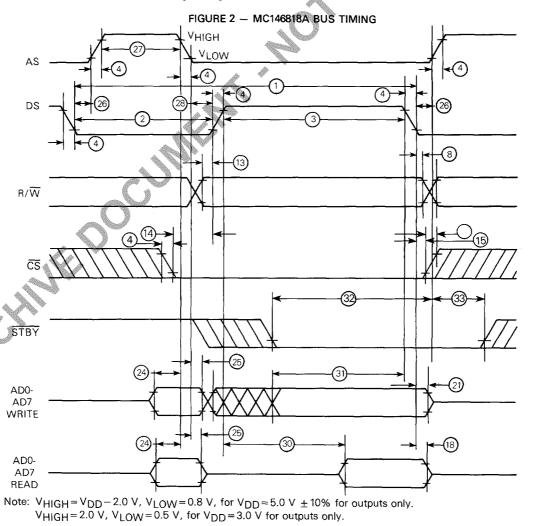

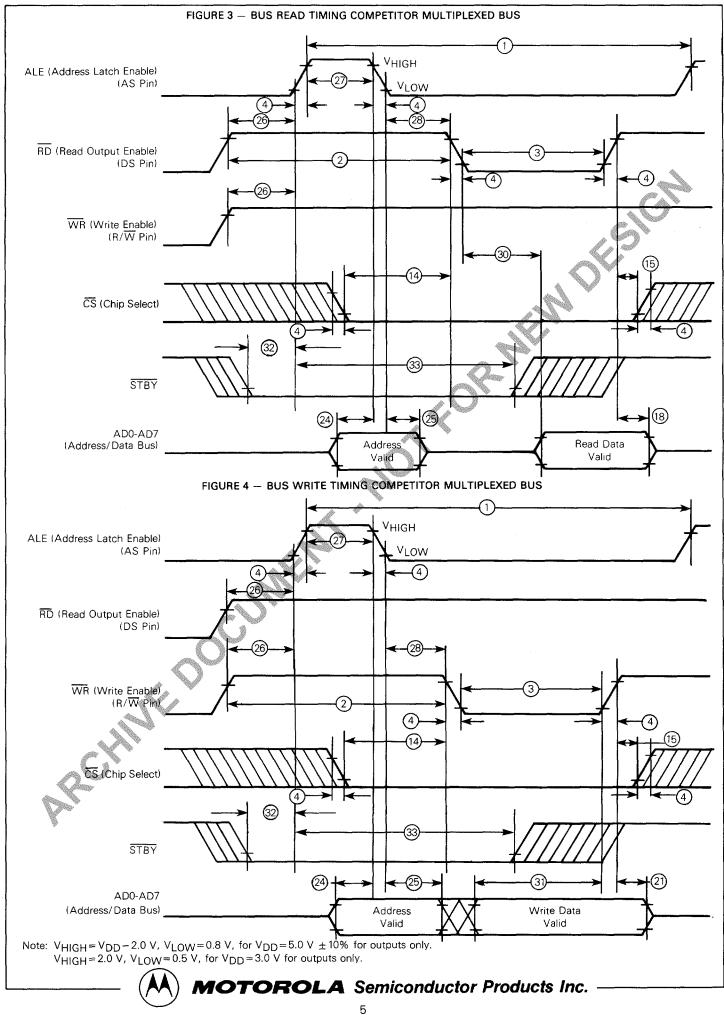

#### **BUS TIMING**

| Ident. | V <sub>DD</sub> =3.0 V<br>50 pF Load              |                                 |      |      |            | V <sub>DD</sub> = 5.0 V<br>± 10%<br>1 TTL and<br>130 pF Load |      |  |

|--------|---------------------------------------------------|---------------------------------|------|------|------------|--------------------------------------------------------------|------|--|

| Number | Characteristics                                   | Symbol                          | Min  | Max  | Min        | Max                                                          | Unit |  |

| 1      | Cycle Time                                        | tcyc                            | 5000 | _    | 953        | dc                                                           | ns   |  |

| 2      | Pulse Width, DS/E Low or RD/WR High               | PWEL                            | 1000 | _    | 300        |                                                              | ns   |  |

| 3      | Pulse Width, DS/E High or RD/WR Low               | PWEH                            | 1500 | _    | 325        | _                                                            | ns   |  |

| 4      | Input Rise and Fall Time                          | t <sub>r</sub> , t <sub>f</sub> |      | 100  |            | 30                                                           | ns   |  |

| 8      | $R/\overline{W}$ Hold Time                        | <sup>t</sup> RWH                | 10   | -    | 10         | _                                                            | ns 🦠 |  |

| 13     | R/W Setup Time Before DS/E                        | tRWS                            | 200  | -    | 80         | _                                                            | ns   |  |

| 14     | Chip Select Setup Time Before DS, WR, or RD       | tcs                             | 200  |      | 25         | _                                                            | ns   |  |

| 15     | Chip Select Hold Time                             | tCH                             | 10   |      | 0          |                                                              | ns   |  |

| 18     | Read Data Hold Time                               | tDHR                            | 10   | 1000 | 10         | 100                                                          | ns   |  |

| 21     | Write Data Hold Time                              | tDHW                            | 100  | _    | 0          | 4 +                                                          | ns   |  |

| 24     | Muxed Address Valid Time to AS/ALE Fall           | †ASL                            | 200  | _    | 50         | -                                                            | ns   |  |

| 25     | Muxed Address Hold Time                           | <sup>t</sup> AHL                | 100  | _    | 20         | W -                                                          | ns   |  |

| 26     | Delay Time DS/E to AS/ALE Rise                    | t <sub>ASD</sub>                | 500  |      | 50         | 1.                                                           | ns   |  |

| 27     | Pulse Width, AS/ALE High                          | PWASH                           | 600  | - /  | 135        | _                                                            | ns   |  |

| 28     | Delay Time, AS/ALE to DS/E Rise                   | †ASED                           | 500  | +    | <i>6</i> 0 |                                                              | ns   |  |

| 30     | Peripheral Output Data Delay Time from DS/E or RD | tDDR                            | 1300 | -    | 20         | 240                                                          | ns   |  |

| 31     | Peripheral Data Setup Time                        | tDSW                            | 1500 | >    | 200        | _                                                            | ns   |  |

| 32     | STBY Setup Time before AS/ALE Rise                | tSBS                            | TBD  | _    | TBD        | _                                                            |      |  |

| 33     | STBY Hold Time after AS/ALE Fall                  | <sup>t</sup> SBH                | TBD  | _    | TBD        | _                                                            |      |  |

NOTE: Designations E, ALE, RD, and WR refer to signals from alternative microprocessor signals.

<sup>\*</sup> Refer to IMPORTANT NOTICES appearing on page 20 of this data sheet.

TABLE 1 — SWITCHING CHARACTERISTICS ( $V_{SS} = 0 \text{ Vdc}$ ,  $T_A = T_L \text{ to } T_H$ )

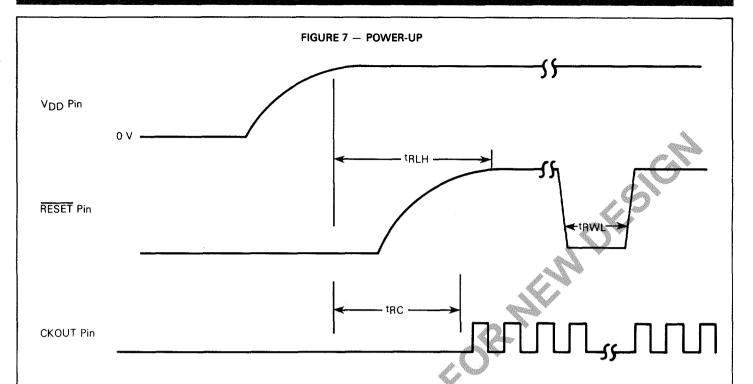

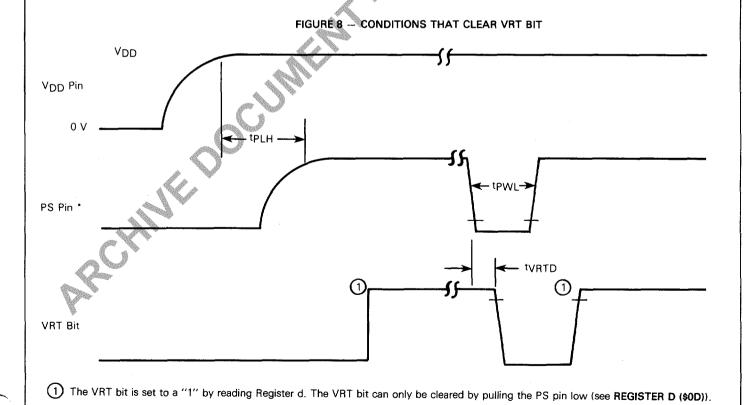

$V_{DD} = 3.0 \text{ Vdc}$  $V_{DD} = 5.0 \text{ Vdc } \pm 10\%$ Description Min Symbol Max Unit Min Max Oscillator Startup TBD tRC ms 100 ms Reset Pulse Width TBD 5 <sup>t</sup>RWL μS μS Reset Delay Time TBD 5 <sup>t</sup>RLH  $\mu$ S μS Power Sense Pulse Width TBD 5 t<sub>PWL</sub> μS μS Power Sense Delay Time TBD 5 t<sub>PLH</sub> μS μs IRQ Release from DS TBD **tIRDS** μS μS IRQ Release from RESET TBD t<sub>IRR</sub> μS μS VRT Bit Delay TBD **tVRTD**  $\mu$ S  $\mu$ S

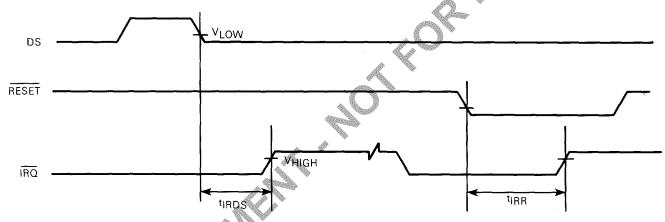

FIGURE 5 - IRQ RELEASE DELAY

NOTE:  $V_{HIGH} = V_{DD} - 2.0 \text{ V}$ ,  $V_{LOW} = 0.8 \text{ V}$ , for  $V_{DD} = 5.0 \text{ V} \pm 10\%$

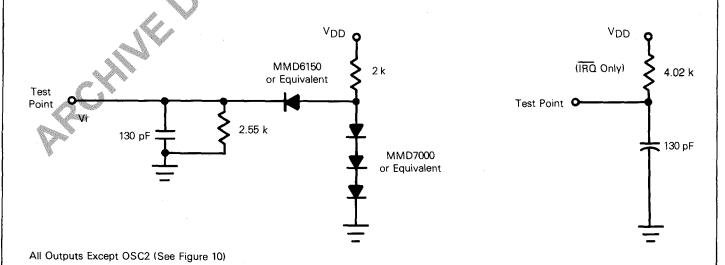

FIGURE 6 - TTL EQUIVALENT TEST LOAD

#### SIGNAL DESCRIPTIONS

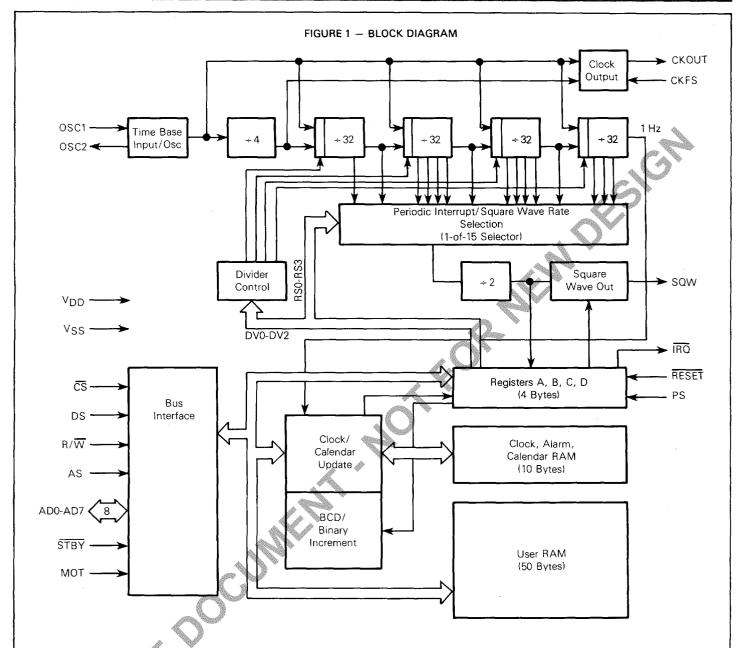

The block diagram in Figure 1, shows the pin connection with the major internal functions of the MC146818A Real-Time Clock plus RAM. The following paragraphs describe the function of each pin.

#### VDD, VSS

DC power is provided to the part on these two pins,  $V_{DD}$  being the more positive voltage. The minimum and maximum voltages are listed in the Electrical Characteristics tables.

#### MOT-MOTEL

The MOT pin offers flexibility when choosing bus type. When tied to V<sub>DD</sub>, Motorola timing is used. When tied to V<sub>SS</sub>, competitor timing is used. The MOT pin must be hardwired to the V<sub>DD</sub> or V<sub>SS</sub> supply and cannot be switched during operation of the MC146818A.

#### OSC1, OSC2 - TIME BASE, INPUTS

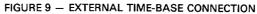

The time base for the time functions may be an external signal or the crystal oscillator. External square waves at 4.194304 MHz, 1.048576 MHz, or 32.768 kHz may be connected to OSC1 as shown in Figure 9. The internal time-base frequency to be used is chosen in Register A.

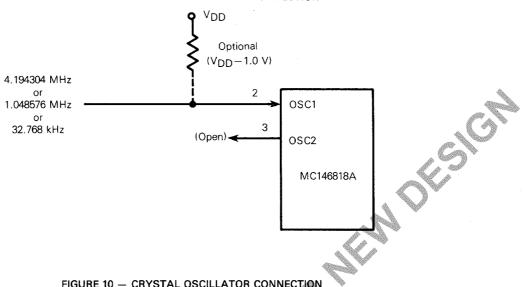

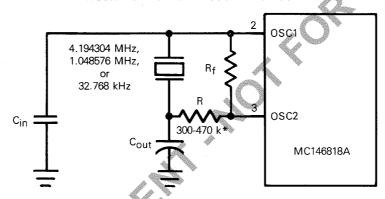

The on-chip oscillator is designed for a parallel resonant AT cut crystal at 4.194304 MHz, 1.048576 MHz or 32.768 kHz frequencies. The crystal connections are shown in Figure 10 and the crystal characteristics in Figure 11.

#### CKOUT - CLOCK OUT, OUTPUT

The CKOUT pin is an output at the time-base frequency divided by 1 or 4. A major use for CKOUT is as the input clock to the microprocessor; thereby saving the cost of a second crystal. The frequency of CKOUT depends upon the time-base frequency and the state of the CKFS pin as shown in Table 2.

#### CKFS - CLOCK OUT FREQUENCY SELECT, INPUT

When the CKFS pin is tied to  $V_{DD}$ , it causes CKOUT to be the same frequency as the time base at the OSC1 pin. When CKFS is tied to  $V_{SS}$ , CKOUT is the OSC1 time-base frequency divided by four. Table 2 summarizes the effect of CKFS.

TABLE 2 — CLOCK OUTPUT FREQUENCIES

| Time Base<br>(OSC1)<br>Frequency | Clock Frequency<br>Select Pin<br>(CKFS) | Clock Frequency<br>Output Pin<br>(CKOUT) |  |  |

|----------------------------------|-----------------------------------------|------------------------------------------|--|--|

| 4.194304 MHz                     | High                                    | 4.194304 MHz                             |  |  |

| 4.194304 MHz                     | Low                                     | 1.048576 MHz                             |  |  |

| 1.048576 MHz                     | High                                    | 1.048576 MHz                             |  |  |

| 1.048576 MHz                     | Low                                     | 262.144 kHz                              |  |  |

| 32.768 kHz                       | High                                    | 32.768 kHz                               |  |  |

| 32.768 kHz                       | Low                                     | 8.192 kHz                                |  |  |

#### SQW — SQUARE WAVE, OUTPUT

The SQW pin can output a signal from one of the 15 taps provided by the 22 internal-divider stages. The frequency of the SQW may be altered by programming Register A, as shown in Table 5. The SQW signal may be turned on and off using the SQWE bit in Register B.

# AD0-AD7 — MULTIPLEXED BIDIRECTIONAL ADDRESS/DATA BUS

Multiplexed bus processors save pins by presenting the address during the first portion of the bus cycle and using the same pins during the second portion for data. Address-then-data multiplexing does not slow the access time of the MC146818A since the bus reversal from address to data is occurring during the internal RAM access time.

The address must be valid just prior to the fall of AS/ALE at which time the MC146818A latches the address from AD0 to AD5. Valid write data must be presented and held stable during the latter portion of the DS or WR pulses. In a read cycle, the MC146818A outputs eight bits of data during the latter portion of the DS or RD pulses, then ceases driving the bus (returns the output drivers to the high-impedance state) when DS falls in the Motorola case of MOTEL or RD rises in the other case.

#### AS - MULTIPLEXED ADDRESS STROBE, INPUT

A positive going multiplexed address strobe pulse serves to demultiplex the bus. The falling edge of AS or ALE causes the address to be latched within the MC146818A.

#### DS - DATA STROBE OR READ, INPUT

The DS pin has two interpretations via the MOTEL circuit. When emanating from a Motorola type processor, DS is a positive pulse during the latter portion of the bus cycle, and is variously called DS (data strobe), E (enable), and  $\phi 2$  ( $\phi 2$  clock). During read cycles, DS signifies the time that the RTC is to drive the bidirectional bus. In write cycles, the trailing edge of DS causes the Real-Time Clock plus RAM to latch the written data.

The second MOTEL interpretation of DS is that of RD, MEMR, or I/OR emanating from the competitor type processor. In this case, DS identifies the time period when the real-time clock plus RAM drives the bus with read data. This interpretation of DS is also the same as an output-enable signal on a typical memory.

### $R/\overline{W}$ - READ/WRITE, INPUT

The MOTEL circuit treats the R/ $\overline{W}$  pin in one of two ways. When a Motorola type processor is connected, R/ $\overline{W}$  is a level which indicates whether the current cycle is a read or write. A read cycle is indicated with a high level on R/ $\overline{W}$  while DS is high, whereas a write cycle is a low on R/ $\overline{W}$  during DS.

The second interpretation of  $R/\overline{W}$  is as a negative write pulse,  $\overline{WR}$ ,  $\overline{MEMW}$ , and  $\overline{I/OW}$  from competitor type processors. The MOTEL circuit in this mode gives  $R/\overline{W}$  pin the same meaning as the write  $(\overline{W})$  pulse on many generic RAMs.

#### CS - CHIP SELECT, INPUT

The chip-select  $(\overline{CS})$  signal must be asserted (low) for a bus cycle in which the MC146818A is to be accessed.  $\overline{CS}$  is not latched and must be stable during DS and AS (Motorola case of MOTEL) and during  $\overline{RD}$  and  $\overline{WR}$ . Bus cycles which take place without asserting  $\overline{CS}$  cause no actions to take place within the MC146818A. When  $\overline{CS}$  is not used, it should be grounded. (See Figure 20).

#### FIGURE 10 - CRYSTAL OSCILLATOR CONNECTION

\*32.768 kHz Only Consult Crystal Manufacturer's Specification

#### FIGURE 11 - CRYSTAL PARAMETERS

Crystal Equivalent Circuit

| . 3 | ii i          | 2 |

|-----|---------------|---|

|     | <b>─</b> ┤  } |   |

| fosc                              | 4.194304 MHz | 1.048576 MHz | 32.768 kHz |

|-----------------------------------|--------------|--------------|------------|

| RS (Maximum)                      | 75 Ω         | 700 Ω        | 50 k       |

| C0 (Maximum)                      | 7 pF         | 5 pF         | 1.7 pF     |

| C1                                | 0.012 pF     | 0.008 pF     | 0.003 pF   |

| Q                                 | 50 k         | 35 k         | 30 k       |

| C <sub>in</sub> /C <sub>out</sub> | 15-30 pF     | 15-40 pF     | 10-22 pF   |

| R                                 | _            | _            | 300-470 k  |

| R <sub>f</sub>                    | 10 M         | 10 M         | 22 M       |

#### IRQ - INTERRUPT REQUEST, OUTPUT

The  $\overline{\text{IRQ}}$  pin is an active low output of the MC146818A that may be used as an interrupt input to a processor. The  $\overline{\text{IRQ}}$  output remains low as long as the status bit causing the interrupt is present and the corresponding interrupt-enable bit is set. To clear the  $\overline{\text{IRQ}}$  pin, the processor program normally reads Register C. The  $\overline{\text{RESET}}$  pin also clears pending interrupts.

When no interrupt conditions are present, the  $\overline{IRQ}$  level is in the high-impedance state. Multiple interrupting devices may thus be connected to an  $\overline{IRQ}$  bus with one pullup at the processor.

#### RESET - RESET, INPUT

The RESET pin does not affect the clock, calendar, or RAM functions. On powerup, the RESET pin must be held low for the specified time, t<sub>RLH</sub>, in order to allow the power supply to stabilize. Figure 12 shows a typical representation of the RESET pin circuit.

When RESET is low the following occurs:

- a) Periodic Interrupt Enable (PIE) bit is cleared to zero,

- b) Alarm Interrupt Enable (AIE) bit is cleared to zero,

- c) Alarm Interrupt Enable (AIE) bit is cleared to zero,

- d) Update ended Interrupt Flag (UF) bit is cleared to zero,

- e) Interrupt Request status Flag (IRQF) bit is cleared to zero.

- f) Periodic Interrupt Flag (PF) bit is cleared to zero,

- g) The part is not accessible.

- h) Alarm Interrupt Flag (AF) bit is cleared to zero,

- i) IRQ pin is in high-impedance state, and

- j) Square Wave output Enable (SQWE) bit is cleared to zero.

#### STBY - STAND-BY

The STBY pin, when active, prevents access to the MC146818A making it ideal for battery back-up applications. Stand-by operation incorporates a transparent latch. After data strobe (DS) goes low (RD or WR rises), STBY is recognized as a valid signal.

The  $\overline{STBY}$  signal is totally asynchronous. Its transparent latch is opened by the falling edge of DS (rising edge of  $\overline{RD}$  or  $\overline{WR}$ ) and clocked by the rising edge of AS (ALE). Therefore, for  $\overline{STBY}$  to be recognized, DS and AS should occur in pairs. When  $\overline{STBY}$  goes low before the falling edge of DS (rising edge of  $\overline{WR}$  or  $\overline{RD}$ ), the current cycle is completed at that edge and the next cycle will not be executed.

#### PS - POWER SENSE, INPUT

The power-sense pin is used in the control of the valid RAM and time (VRT) bit in Register D. When the PS pin is low the VRT bit is cleared to zero.

When using the VRT feature during powerup, the PS pin must be externally held low for the specified tp\_H time. As power is applied, the VRT bit remains low indicating that the contents of the RAM, time registers, and calendar are not guaranteed. PS must go high after powerup to allow the VRT bit to be set by a read of register D.

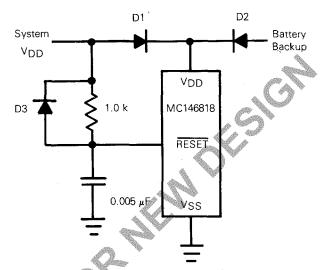

# FIGURE 12—TYPICAL POWERUP DELAY CIRCUIT FOR RESET

D1 = MBD701 (Schottky) or Equivalent D2 = D3 = 1N4148 or Equivalent

Note: If the RTC is isolated from the MPU or MCU power by a diode drop, care must be taken to meet V<sub>in</sub> requirements.

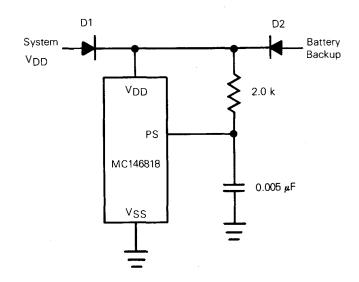

# FIGURE 13 — TYPICAL POWERUP DELAY CIRCUIT FOR POWER SENSE

D1 = MBD701 (Schottky) or Equivalent D2 = 1N4148 or Equivalent

#### POWER-DOWN CONSIDERATIONS

In most systems, the MC146818A must continue to keep time when system power is removed. In such systems, a conversion from system power to an alternate power supply, usually a battery, must be made. During the transition from system to battery power, the designer of a battery backed-up RTC system must protect data integrity, minimize power consumption, and ensure hardware reliability.

The stand-by (STBY) pin controls all bus inputs (R/W, DS, AS, AD0-AD7) STBY, when negated, disallows any unintended modification of the RTC data by the bus. STBY also reduces power consumption by reducing the number of transitions seen internally.

Power consumption may be further reduced by removing resistive and capacitive loads from the clock out (CKOUT) pin and the squarewave (SQW) pin.

During and after the power source conversion, the  $V_{IN}$  maximum specification must never be exceeded. Failure to meet the  $V_{IN}$  maximum specification can cause a virtual SCR to appear which may result in excessive current drain and destruction of the part.

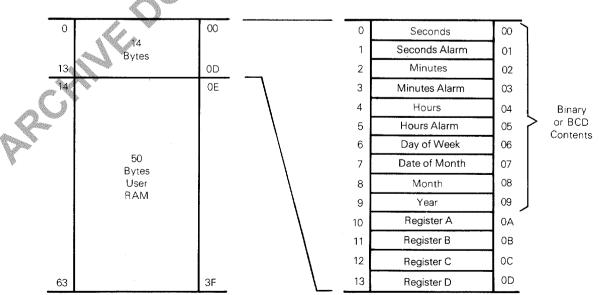

#### ADDRESS MAP

Figure 14 shows the address map of the MC146818A. The memory consists of 50 general purpose RAM bytes, 10 RAM bytes which normally contain the time, calendar, and alarm data, and four control and status bytes. All 64 bytes are directly readable and writable by the processor program except for the following: 1) Registers C and D are read only, 2) bit 7 of Register A is read only, and 3) the high-order bit of the seconds byte is read only. The contents of four control and status registers (A, B, C, and D) are described in **REGISTERS.**

#### TIME, CALENDAR, AND ALARM LOCATIONS

The processor program obtains time and calendar information by reading the appropriate locations. The program may initialize the time, calendar, and alarm by writing to these RAM locations. The contents of the 10 time, calendar, and alarm bytes may be either binary or binary-coded decimal (BCD).

Before initializing the internal registers, the SET bit in Register B should be set to a "1" to prevent time/calendar updates from occurring. The program initializes the 10 locations in the selected format (binary or BCD), then indicates the format in the data mode (DM) bit of Register B. All 10 time, calendar, and alarm bytes must use the same data mode, either binary or BCD. The SET bit may now be cleared to allow updates. Once initialized the real-time clock makes all updates in the selected data mode. The data mode cannot be changed without reinitializing the 10 data bytes.

Table 3 shows the binary and BCD formats of the 10 time, calendar, and alarm locations. The 24/12 bit in Register B establishes whether the hour locations represent 1-to-12 or 0-to-23. The 24/12 bit cannot be changed without reinitializing the hour locations. When the 12-hour format is selected the high-order bit of the hours byte represents PM when it is a "1".

The time, calendar, and alarm bytes are not always accessible by the processor program. Once per second the 10 bytes are switched to the update logic to be advanced by one second and to check for an alarm condition. If any of the 10 bytes are read at this time, the data outputs are undefined. The update lockout time is 248  $\mu$ s at the 4.194304 MHz and 1.048667 MHz time bases and 1948  $\mu$ s for the 32.768 kHz time base. The Update Cycle section shows how to accommodate the update cycle in the processor program.

The three alarm bytes may be used in two ways. First, when the program inserts an alarm time in the appropriate hours, minutes, and seconds alarm locations, the alarm interrupt is initiated at the specified time each day if the alarm enable bit is high. The second usage is to insert a "don't care" state in one or more of three alarm bytes. The "don't care" code is any hexadecimal byte from CO to FF. That is, the two most-significant bits of each byte, when set to "1", create a "don't care" situation. An alarm interrupt each hour is created with a "don't care" code in the hours alarm location. Similarly, an alarm is generated every minute with "don't care" codes in the hours and minutes alarm bytes. The "don't care" codes in all three alarm bytes create an interrupt every second.

FIGURE 14 - ADDRESS MAP

TABLE 3 - TIME, CALENDAR, AND ALARM DATA MODES

| A al al             |                               | Danimal          |                                      |                                      | Exan                | nple*            |

|---------------------|-------------------------------|------------------|--------------------------------------|--------------------------------------|---------------------|------------------|

| Address<br>Location | Function                      | Decimal<br>Range | Binary Data Mode                     | nge<br>BCD Data Mode                 | Binary<br>Data Mode | BCD<br>Data Mode |

| 0                   | Seconds                       | 0-59             | \$00-\$3B                            | \$00-\$59                            | 15                  | 21               |

| 1                   | Seconds Alarm                 | 0-59             | \$00-\$3B                            | \$00-\$59                            | 15                  | 21               |

| 2                   | Minutes                       | 0-59             | \$00-\$3B                            | \$00-\$59                            | 3A                  | 58               |

| 3                   | Minutes Alarm                 | 0-59             | \$00-\$3B                            | \$00-\$59                            | 3A                  | 58               |

|                     | Hours<br>(12 Hour Mode)       | 1-12             | \$01-\$0C (AM) and<br>\$81-\$8C (PM) | \$01-\$12 (AM) and<br>\$81-\$92 (PM) | 05                  | 05               |

| 4                   | Hours<br>(24 Hour Mode)       | 0-23             | \$00-\$17                            | \$00-\$23                            | 05                  | 05               |

| 5                   | Hours Alarm<br>(12 Hour Mode) | 1-12             | \$01-\$0C (AM) and<br>\$81-\$8C (PM) | \$01-\$12 (AM) and<br>\$81-\$92 (PM) | 05                  | 05               |

| ŭ                   | Hours Alarm<br>(24 Hour Mode) | 0-23             | \$00-\$17                            | \$00-23                              | 05                  | 05               |

| 6                   | Day of the Week<br>Sunday=1   | 1-7              | \$01-\$ 07                           | \$01-\$07                            | 05                  | 05               |

| 7                   | Date of the Month             | 1-31             | \$01-\$1F                            | \$01-\$31                            | OF                  | 15               |

| 8                   | Month                         | 1-12             | \$01-\$0C                            | \$01-\$12                            | 02                  | 02               |

| 9                   | Year                          | 0-99             | \$00-\$63                            | \$00-\$99                            | ₹ 4F                | 79               |

<sup>\*</sup>Example: 5:58:21 Thursday 15 February 1979 (time is AM)

#### STATIC CMOS RAM

The 50 general purpose RAM bytes are not dedicated within the MC146818A. They can be used by the processor program, and are fully available during the update cycle.

When time and calendar information must use battery back-up, very frequently there is other non-volatile data that must be retained when main power is removed. The 50 user RAM bytes serve the need for low-power CMOS battery-backed storage, and extend the RAM available to the program.

When further CMOS RAM is needed, additional MC146818As may be included in the system. The time/calendar functions may be disabled by holding the DV0-DV2 dividers, in Register A, in the reset state by setting the SET bit in Register B or by removing the oscillator. Holding the dividers in reset prevents interrupts or SQW output from operating while setting the SET bit allows these functions to occur. With the dividers clear, the available user RAM is extended to 59 bytes. The high-order bit of the seconds byte, bit 7 of Register A, and all bits of Registers C and D cannot effectively be used as general purpose RAM.

#### INTERRUPTS

The RTC plus RAM includes three separate fully automatic sources of interrupts to the processor. The alarm interrupt may be programmed to occur at rates from once-per-second to one-a-day. The periodic interrupt may be selected for rates from half-a-second to 30.517  $\mu$ s. The update-ended interrupt may be used to indicate to the program that an update cycle is completed. Each of these independent interrupt conditions are described in greater detail in other sections.

The processor program selects which interrupts, if any, it wishes to receive. Three bits in Register B enable the three interrupts. Writing a "1" to a interrupt-enable bit permits that interrupt to be initiated when the event occurs. A "0" in the interrupt-enable bit prohibits the IRQ pin from being asserted due to the interrupt cause.

If an interrupt flag is already set when the interrupt becomes enabled, the  $\overline{\text{IRQ}}$  pin is immediately activiated, though the interrupt initiating the event may have occurred much earlier. Thus, there are cases where the program should clear such earlier initiated interrupts before first enabling new interrupts.

When an interrupt event occurs, a flag bit is set to a "1" in Register C. Each of the three interrupt sources have separate flag bits in Register C, which are set independent of the state of the corresponding enable bits in Register B. The flag bit may be used with or without enabling the corresponding enable bits.

In the software scanned case, the program does not enable the interrupt. The "interrupt" flag bit becomes a status bit, which the software interrogates, when it wishes. When the software detects that the flag is set, it is an indication to software that the "interrupt" event occurred since the bit was last read.

However, there is one precaution. The flag bits in Register C are cleared (record of the interrupt event is erased) when Register C is read. Double latching is included with Register C so the bits which are set are stable throughout the read cycle. All bits which are high when read by the program are cleared, and new interrupts (on any bits) are held after the read cycle. One, two or three flag bits may be found to be set when Register C is used. The program should inspect all utilized flag bits every time Register C is read to insure that no interrupts are lost.

The second flag bit usage method is with fully enabled interrupts. When an interrupt-flag bit is set and the corresponding interrupt-enable bit is also set, the  $\overline{\mbox{IRQ}}$  pin is asserted low.  $\overline{\mbox{IRQ}}$  is asserted as long as at least one of the three interrupt sources has its flag and enables bits both set. The IRQF bit in Register C is a "1" whenever the  $\overline{\mbox{IRQ}}$  pin is being driven low.

The processor program can determine that the RTC initiated the interrupt by reading Register C. A "1" in bit 7

(IRQF bit) indicates that one or more interrupts have been initiated by the part. The act of reading Register C clears all the then-active flag bits, plus the IRQF bit. When the program finds IRQF set, it should look at each of the individual flag bits in the same byte which have the corresponding interrupt-mask bits set and service each interrupt which is set. Again, more than one interrupt-flag bit may be set.

#### **DIVIDER STAGES**

The MC146818A has 22 binary-divider stages following the time base as shown in Figure 1. The output of the dividers is a 1 Hz signal to the update-cycle logic. The divers are controlled by three divider bus (DV2, DV1, and DV0) in Register A.

#### **DIVIDER CONTROL**

The divider-control bits have three uses, as shown in Table 4. Three usable operating time bases may be selected (4.194304 MHz, 1.048576 MHz, or 32.768 kHz). The divider chain may be held at reset, which allows precision setting of the time, When the divider is changed from reset to an

operating time base, the first update cycle is one-half second later. The divider-control bits are also used to facilitate testing the MC146818A.

#### SQUARE-WAVE OUTPUT SELECTION

Fifteen of the 22 divider taps are made available to a 1-of-15 selector as shown in Figure 1. The first purpose of selecting a divider tap is to generate a square-wave output signal at the SQW pin. The RS0-RS3 bits in Register A establish the square-wave frequency as listed in Table 5. The SQW frequency selection shares the 1-of-15 selector with periodic interrupts.

Once the frequency is selected, the output of the SQW pin may be turned on and off under program control with the square-wave output selection bits, or the SQWE output-enable bit may generate an asymmetrical waveform at the time of execution. The square-wave output pin has a number of potential uses. For example, it can serve as a frequency standard for external use, a frequency synthesizer, or could be used to generate one or more audio tones under program control.

**TABLE 4 — DIVIDER CONFIGURATIONS**

| Time-Base<br>Frequency | Divider Bits<br>Register A |     |     | Operation<br>Mode | Divider<br>Reset | Bypass First<br>N-Divider Bits |

|------------------------|----------------------------|-----|-----|-------------------|------------------|--------------------------------|

|                        | DV2                        | DV1 | DV0 |                   |                  |                                |

| 4.194304 MHz           | 0                          | 0   | 0   | Yes               |                  | N = 0                          |

| 1.048576 MHz           | 0                          | 0   | 1   | Yes               |                  | N = 2                          |

| 32.768 kHz             | 0                          | 1   | 0   | Yes               | _                | N = 7                          |

| Any                    | 1                          | 1   | 0   | No                | Yes              |                                |

| Any                    | 1                          | · 1 | 1   | No                | Yes              |                                |

Note: Other combinations of divider bits are used for test purposes only.

TABLE 5 — PERIODIC INTERRUPT RATE AND SQUARE WAVE OUTPUT FREQUENCY

|      |                                         | Calac   | t Dita                |            |                            | .048576 MHz<br>Base |             | 8 kHz<br>Base |  |

|------|-----------------------------------------|---------|-----------------------|------------|----------------------------|---------------------|-------------|---------------|--|

|      | Select Bits Register A  RS3 RS2 RS1 RS0 |         | Periodic   SQW Output |            | Periodic<br>Interrupt Rate | SQW Output          |             |               |  |

|      |                                         | 1,102   | -101                  |            | tPI                        | Frequency           | tPI         | Frequency     |  |

| ٩    | 0                                       | 0       | 0                     | 0          | None                       | None                | None        | None          |  |

| Dig. | Ò                                       | 0       | 0                     | 1          | 30.517 μs                  | 32.768 kHz          | 3.90625 ms  | 256 Hz        |  |

| >    | 0                                       | 0       | 1                     | 0          | 61.035 μs                  | 16.384 kHz          | 7.8125 ms   | 128 Hz        |  |

|      | 0                                       | 0 0 1 1 |                       | 122.070 μs | 8.192 kHz                  | 122.070 μs          | 8.192 kHz   |               |  |

| I    | 0                                       | 1       | 0                     | 0          | 244.141 μs                 | 4.096 kHz           | 244.141 μs  | 4.096 kHz     |  |

| 1    | 0                                       | 1       | 0                     | 1          | 488.281 μs                 | 2.048 kHz           | 488.281 μs  | 2.048 kHz     |  |

|      | 0                                       | 1       | 1                     | 0          | 976.562 μs                 | 1.024 kHz           | 976.562 μs  | 1.024 kHz     |  |

| ı    | 0                                       | 1       | 1                     | 1          | 1.953125 ms                | 512 Hz              | 1.953125 ms | 512 Hz        |  |

|      | 1                                       | 0       | 0                     | 0          | 3.90625 ms                 | 256 Hz              | 3.90625 ms  | 256 Hz        |  |

|      | 1                                       | 0       | 0                     | 1          | 7.8125 ms                  | 128 Hz              | 7.8125 ms   | 128 Hz        |  |

|      | 1                                       | 0       | 1                     | 0          | 15.625 ms                  | 64 Hz               | 15.625 ms   | 64 Hz         |  |

|      | 1                                       | 0       | 1                     | 1          | 31.25 ms                   | 32 Hz               | 31.25 ms    | 32 Hz         |  |

|      | 1                                       | 1       | 0                     | 0          | 62.5 ms                    | 16 Hz               | 62.5 ms     | 16 Hz         |  |

|      | 1                                       | 1       | 0                     | 1          | 125 ms                     | 8 Hz                | 125 ms      | 8 Hz          |  |

|      | 1                                       | 1       | 1                     | 0          | 250 ms                     | 4 Hz                | 250 ms      | 4 Hz          |  |

|      | 1                                       | 1       | 1                     | 1          | 500 ms                     | 2 Hz                | 500 ms      | 2 Hz          |  |

#### PERIODIC INTERRUPT SELECTION

The periodic interrupt allows the  $\overline{\text{IRQ}}$  pin to be triggered from once every 500 ms to once every 30.517  $\mu s$ . The periodic interrupt is separate from the alarm interrupt which may be output from once per second to once per day.

Table 5 shows that the periodic interrupt rate is selected with the same Register A bits which select the square-wave frequency. Changing one also changes the other. But each function may be separately enabled so that a program could switch between the two features or use both. The SQW pin is enabled by the SQWE bit in Register B. Similarly the periodic interrupt is enabled by the PIE bit in Register B.

Periodic interrupt is usable by practically all real-time systems. It can be used to scan for all forms of inputs from contact closures to serial recieve bits or bytes. It can be used in multiplexing displays or with software counters to measure inputs, create output intervals, or await the next needed software function.

#### **UPDATE CYCLE**

The MC146818A executes an update cycle once per second, assuming one of the proper time bases is in place, the DV0-DV2 divider is not clear, and the SET bit in Register B is clear. The SET bit in the "1" state permits the program to initialize the time and calendar bytes by stopping an existing update and preventing a new one from occurring.

The primary function of the update cycle is to increment the seconds byte, check for overflow, increment the minutes byte when appropriate and so forth through to the year of the century byte. The update cycle also compares each alarm byte with the corresponding time byte and issues an alarm if a match or if a "don't care" code (11XXXXXX) is present in all three positions.

With a 4.194304 MHz or 1.048576 MHz time base the update cycle takes 248  $\mu$ s while a 32.768 kHz time base update cycle takes 1984  $\mu$ s. During the update cycle, the time, calendar, and alarm bytes are not accessible by the processor program. The MC146818A protects the program from reading transitional data. This protection is provided by switching the time, calendar, and alarm portion of the RAM off the microprocessor bus during the entire update cycle. If the processor reads these RAM locations before the update is

complete, the output will be undefined. The update in progress (UIP) status bit is set during the interval.

A program which randomly accesses the time and date information finds data unavailable statistically once every 4032 attempts. Three methods of accommodating nonavailability during update are usable by the program. In discussing the three methods, it is assumed that at random points user programs are able to call a subroutine to obtain the time of day.

The first method of avoiding the update cycle uses the update-ended interrupt. If enabled, an interrupt occurs after every update cycle which indicates that over 999 ms are available to read valid time and date information. During this time a display could be updated or the information could be transferred to continuously available RAM. Before leaving the interrupt service routine, the IRQF bit in Register C should be cleared.

The second method uses the update-in-progress bit (UIP) in Register A to determine if the update cycle is in progress or not. The UIP bit will pulse once per second. Statistically, the UIP bit will indicate that time and date information is unavailable once every 2032 attempts. After the UIP bit goes high, the update cycle begins 244  $\mu s$  later. Therefore, if a low is read on the UIP bit, the user has at least 244  $\mu s$  before the time/calendar data will be changed. If a "1" is read in the UIP bit, the time/calendar data may not be valid. The user should avoid interrupt service routines that would cause the time needed to read valid time/calendar data to exceed 244  $\mu s$ .

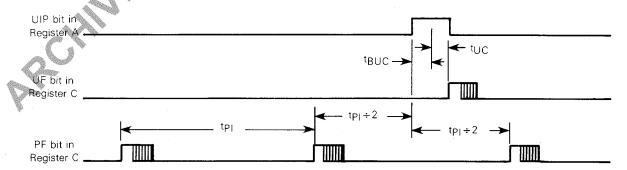

The third method uses a periodic interrupt to determine if an update cycle is in progress. The UIP bit in Register A is set high between the setting of the PF bit in Register C (see Figure 15). Periodic interrupts that occur at a rate of greater than  $t_{\text{BUC}} + t_{\text{UC}}$  allow valid time and date information to be read at each occurrence of the periodic interrupt. The reads should be completed within  $(T_{\text{PI}} + 2) + t_{\text{BUC}}$  to ensure that data is not read during the update cycle.

To properly setup the internal counters for daylight savings time operation, the user must set the time at least two seconds before the rollover will occur. Likewise, the time must be set at least two seconds before the end of the 29th or 30th day of the month.

#### FIGURE 15 — UPDATE-ENDED AND PERIODIC INTERRUPT RELATIONSHIP

tp<sub>1</sub> = Periodic Interrupt Time Interval (500 ms, 250 ms, 125 ms, 62.5 ms, etc. per Table 5)

$t_{UC}$  = Update Cycle Time (248  $\mu$ s or 1984  $\mu$ s)

$t_{BUC}$  = Delay Time Before Update Cycle (244  $\mu$ s)

#### REGISTERS

The MC146818A has four registers which are accessible to the processor program. The four registers are also fully accessible during the update cycle.

#### REGISTER A (\$0A)

| MSB |     | LSB | Read/Write |     |     |     |     |            |

|-----|-----|-----|------------|-----|-----|-----|-----|------------|

| b7  | b6  | b5  | b4         | b3  | b2  | b1  | b0  | Register   |

| UIP | DV2 | DV1 | DV0        | RS3 | RS2 | RS1 | RS0 | except UIP |

UIP — The update in progress (UIP) bit is a status flag that may be monitored by the program. When UIP is a "1", the update cycle is in progress or will soon begin. When UIP is a "0", the update cycle is not in progress and will not be for at least 244  $\mu s$  (for all time bases). This is detailed in Table 6. The time, calendar, and alarm information in RAM is fully available to the program when the UIP bit is zero — it is not in transition. The UIP bit is a read-only bit, and is not affected by Reset. Writing the SET bit in Register B to a "1" inhibits any update cycle and then clears the UIP status bit.

TABLE 6 - UPDATE CYCLE TIMES

| TABLE 0 — OF DATE CICLE THRES |                     |                                         |                                               |  |  |  |  |

|-------------------------------|---------------------|-----------------------------------------|-----------------------------------------------|--|--|--|--|

| UIP Bit                       | Time Base<br>(OSC1) | Update Cycle Time<br>(t <sub>UC</sub> ) | Minimum Time<br>Before Update<br>Cycle (tBUC) |  |  |  |  |

| 1                             | 4.194304 MHz        | 248 μs                                  | _                                             |  |  |  |  |

| 1                             | 1.048576 MHz        | 248 μs                                  | _                                             |  |  |  |  |

| 1                             | 32.768 kHz          | 1984 μs                                 | _                                             |  |  |  |  |

| 0                             | 4.194304 MHz        | _                                       | 244 μs                                        |  |  |  |  |

| 0                             | 1.048576 MHz        | _                                       | 244 μs                                        |  |  |  |  |

| 0                             | 32.768 kHz          | _                                       | 244 μs                                        |  |  |  |  |

|                               |                     |                                         |                                               |  |  |  |  |

DV2, DV1, DV0 — Three bits are used to permit the program to select various conditions of the 22-stage divider chain. The divider selection bits identify which of the three time-base frequencies is in use. Table 4 shows that time bases of 4.194304 MHz, 1.048576 MHz, and 32.768 kHz may be used. The divider selection bits are also used to reset the divider chain. When the time/calendar is first initialized, the program may start the divider at the precise time stored in the RAM. When the divider reset is removed, the first update cycle begins one-half second later. These three read/write bits are not affected by RESET.

RS3, RS2, RS1, RS0 — The four rate selection bits select one of 15 tapes on the 22-stage divider, or disable the divider output. The tap selected may be used to generate an output square wave (SQW pin) and/or a periodic interrupt. The program may do one of the following: 1) enable the interrupt with, the PIE bit, 2) enable the SQW output pin with the SQWE bit, 3) enable both at the same time at the same rate, or 4) enable neither. Table 5 lists the periodic interrupt rates and the square-wave frequencies that may be chosen with the RS bits. These four bits are read/write bits which are not affected by RESET.

#### REGISTER B (\$0B)

| MSB LSB |     |     |     |     |      |    |       | D = = d (1A/=:+ |                       |

|---------|-----|-----|-----|-----|------|----|-------|-----------------|-----------------------|

|         | b7  | b6  | b5  | b4  | b3   | b2 | b1    | ь0              | Read/Write<br>Registe |

|         | SET | PIE | AIE | UIE | SQWE | DM | 24/12 | DSE             |                       |

**SET** — When the SET bit is a "0", the update cycle functions normally by advancing the counts once-per-second. When the SET bit is written to a "1", any update cycle in

progress is aborted and the program may initialize the time and calendar bytes without an update occurring in the midst of initializing. SET is a read/write bit which is not modified by RESET or internal functions of the MC146818A.

**PIE** — The periodic interrupt enable (PIE) bit is a read/write bit which allows the periodic-interrupt flag (PF) bit in Register C to cause the  $\overline{\text{IRQ}}$  pin to be driven low. A program writes a "1" to the PIE bit in order to receive periodic interrupts at the rate specified by the RS3, RS2, RS1, and RS0 bits in Register A. A zero in PIE blocks  $\overline{\text{IRQ}}$  from being initiated by a periodic interrupt, but the periodic flag (PF) bit is still set at the periodic rate. PIE is not modified by any internal MC146818A functions, but is cleared to "0" by a RESET.

AIE — The alarm interrupt enable (AIE) bit is a read/write bit which when set to a "1" permits the alarm flag (AF) bit in Register C to assert  $\overline{\text{IRO}}$ . An alarm interrupt occurs for each second that the three time bytes equal the three alarm bytes (including a "don't care" alarm code by binary 11XXXXX). When the AIE bit is a "0", the AF bit does not initiate an  $\overline{\text{IRO}}$  signal. The  $\overline{\text{RESET}}$  pin clears AIE to "0". The internal functions do not affect the AIE bit.

**UIE** — The UIE (update ended interrupt enable) bit is a read/write bit which enables the update-end flag (UF) bit in Register C to assert  $\overline{\text{IRQ}}$ . The  $\overline{\text{RESET}}$  pin going low or the SET bit going high clears the UIE bit.

**SQWE** When the square-wave enable (SQWE) bit is set to a "1" by the program, a square-wave signal at the frequency specified in the rate selection bits (RS3 to RS0) appears on the SQW pin. When the SQWE bit is set to a zero the SQW pin is held low. The state of SQWE is cleared by the RESET pin. SQWE is a read/write bit.

**DM** — The data mode (DM) bit indicates whether time and calendar updates are to use binary or BCD formats. The DM bit is written by the processor program and may be read by the program, but is not modified by any internal functions or RESET. A "1" in DM signifies binary data, while a "0" in DM specifies binary-coded-decimal (BCD) data.

**24/12** — The 24/12 control bit establishes the format of the hours bytes as either the 24-hour mode (a "1") or the 12-hour mode (a "0"). This is a read/write bit, which is affected only by software.

**DSE** — The daylight savings enable (DSE) bit is a read/write bit which allows the program to enable two special updates (when DSE is a "1"). On the last Sunday in April the time increments from 1:59:59 AM to 3:00:00 AM. On the last Sunday in October when the time first reaches 1:59:59 AM it changes to 1:00:00 AM. These special updates do not occur when the DSE bit is a "0". DSE is not changed by any internal operations or reset.

#### REGISTER C (\$0C)

| MSB LSB |      |    |    |    |    |   |    | Read-Only |          |

|---------|------|----|----|----|----|---|----|-----------|----------|

|         | b7   | b6 | b5 | b4 | b3 | b | b1 | b0        | Register |

|         | IRQF | PF | AF | UF | 0  | 0 | 0  | 0         |          |

**IRQF** — The interrupt request flag (IRQF) is set to a "1" when one or more of the following are true:

PF = PIE = "1"

AF= AIE="1"

UF=UIE="1"

i.e., IRQF = PF•PIE + AF•AIE + UF•UIE

Any time the IRQF bit is a "1", the IRQ pin is driven low. All flag bits are cleared after Register C is read by the program or when the RESET pin is low.

**PF** — The periodic interrupt flag (PF) is a read-only bit which is set to a "1" when a particular edge is detected on the selected tap of the divider chain. The RS3 to RS0 bits establish the periodic rate. PF is set to a "1" independent of the state of the PIE bit. PF being a "1" initiates an  $\overline{\rm IRQ}$  signal and sets the IRQF bit when PIE is also a "1". The PF bit is cleared by a  $\overline{\rm RESET}$  or a software read of Register C.

AF-A "1" in the AF (alarm interrupt flag) bit indicates that the current time has matched the alarm time. A "1" in the AF causes the  $\overline{IRQ}$  pin to go low, and a "1" to appear in the IRQF bit, when the AIE bit also is a "1." A RESET or a read of Register C clears AF.

**UF** — The update-ended interrupt flag (UF) bit is set after each update cycle. when the UIE bit is a "1", the "1" in UF causes the IRQF bit to be a "1", asserting  $\overline{\text{IRQ}}$ . UF is cleared by a Register C read or a  $\overline{\text{RESET}}$ .

b3 TO b0 — The unused bits of Status Register 1 are read as "0's". They can not be written.

#### REGISTER D (\$0D)

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

| VRT | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

VRT — The valid RAM and time (VRT) bit indicates the condition of the contents of the RAM, provided the power sense (PS) pin is satisfactorily connected. A "0" appears in the VRT bit when the power-sense pin is low. The processor program can set the VRT bit when the time and calendar are initialized to indicate that the RAM and time are valid. The VRT is a read only bit which is not modified by the RESET pin. The VRT bit can only be set by reading Register D.

$b6\ T0\ b0$  — The remaining bits of Register D are unused. They cannot be written, but are always read as "0's."

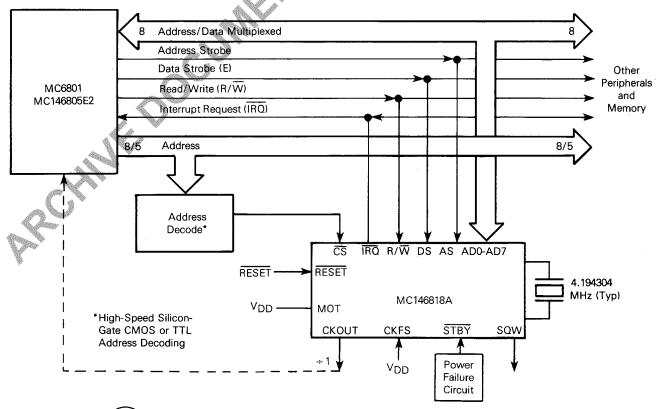

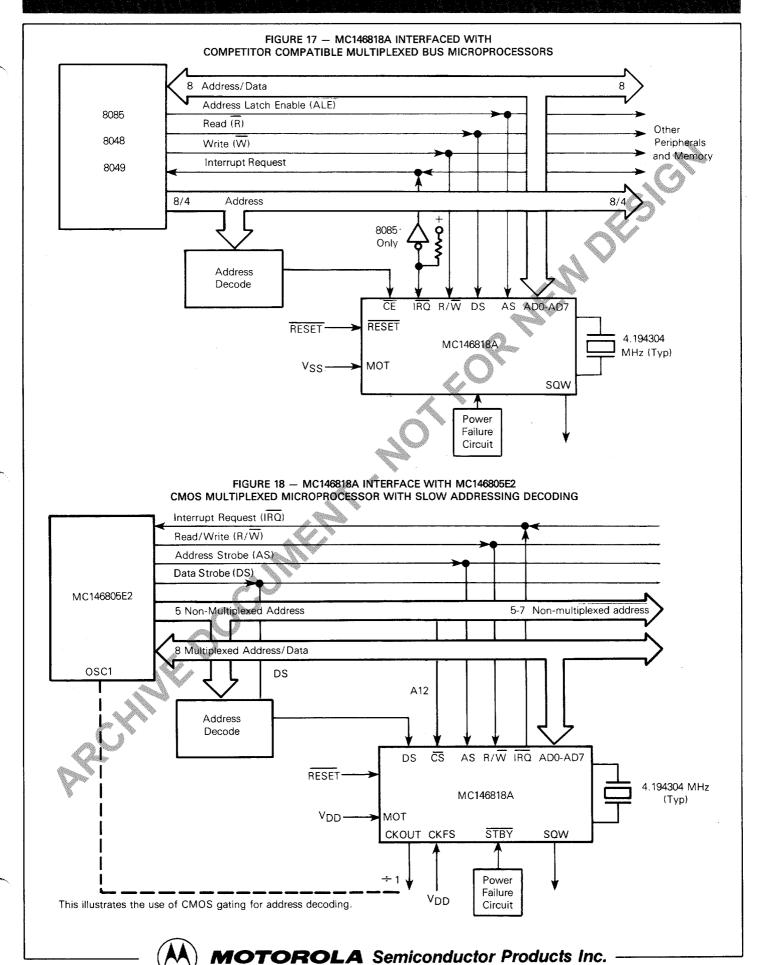

#### TYPICAL INTERFACING

The MC146818A is best suited for use with microprocessors which generate an address-then-data multiplexed bus. Figures 16 and 17 show typical interfaces to bus-compatible processors. These interfaces assume that the address decoding can be done quickly. However, if standard metalgate CMOS gates are used, the  $\overline{\text{CS}}$  setup time may be violated. Figure 18 illustrates an alternative method of chip selection which will accommodate such slower decoding.

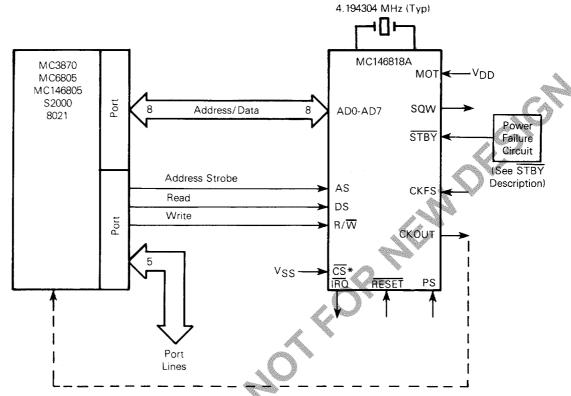

The MC146818A can be interfaced to single-chip microcomputers (MCU) by using eleven port lines as shown in Figure 19. Non-multiplexed bus microprocessors can be interfaced with additional support.

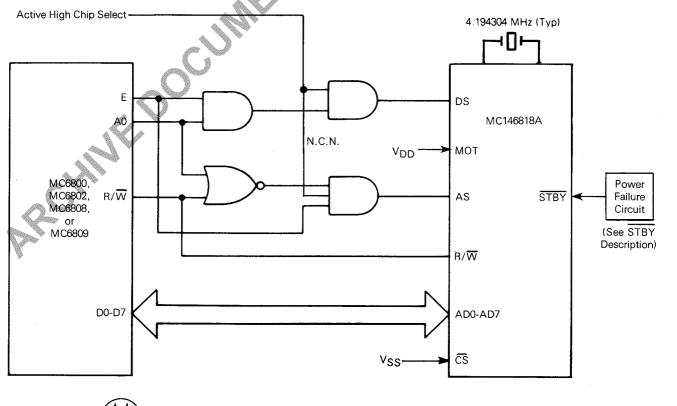

There is one method of using the multiplexed bus MC146818A with non-multiplexed bus processors. The interface uses available bus control signals to multiplex the address and data bus together.

An example using either the Motorola MC6800, MC6802, MC6808, or MC6809 microprocessor is shown in Figure 20. When the MC146818A is I/O mapped as shown in Figures 19 and 20, the AS and DS inputs should be left in a <u>low state</u> when the part is not being accessed. Refer to the <u>STBY</u> pin <u>description</u> for the conditions which must be met before <u>STBY</u> can be recognized.

Figure 21 illustrates the subroutines which may be used for data transfers in a non-multiplexed system. The subroutines should be entered with the registers containing the following data:

Accumulator A: The address of the RTC to be accessed.

Accumulator B: Write: The data to be written.

Read: The data read from the RTC.

The RTC is mapped to two consecutive memory locations — RTC and RTC+1 as shown in Figure 20.

# FIGURE 16 MC146818A INTERFACED WITH MOTOROLA COMPATIBLE MULTIPLEXED BUS MICROPROCESSORS

Read Only

Register

**MOTOROLA** Semiconductor Products Inc.

# FIGURE 19 — MC146818A INTERFACED WITH THE PORTS OF A TYPICAL SINGLE CHIP MICROCOMPUTER

\*NOTE:  $\overline{CS}$  can be controlled by a port pin (if available).

FIGURE 20 — MC146818A INTERFACED WITH MOTOROLA PROCESSORS

# RECHINE DOCUMENT PROPERTY OF THE PROPERTY OF T FIGURE 21 — SUBROUTINE FOR READING AND WRITING THE MC146818A WITH A NON-MULTIPLEXED BUS

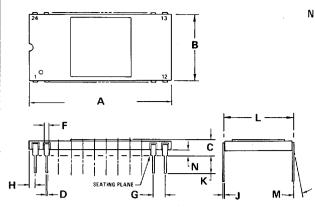

#### PACKAGE DIMENSIONS

#### NOTE:

- 1. LEADS TRUE POSITIONED WITHIN 0.25mm (0.010) DIA (AT SEATING PLANE) AT MAXIMUM MATERIAL CONDITION.

- 2. DIM "L" TO CENTER OF LEADS WHEN FORMED PARALLEL.

|                         | MILLIN | METERS          | INC   | HES   |  |  |  |

|-------------------------|--------|-----------------|-------|-------|--|--|--|

| DIM                     | MIN    | MAX             | MIN   | MAX   |  |  |  |

| Α                       | 27.64  | 30.99           | 1.088 | 1.220 |  |  |  |

| В                       | 14.73  | 15.34           | 0.580 | 0.604 |  |  |  |

| C                       | 2.67   | 4.32            | 0.105 | 0.170 |  |  |  |

| D                       | 0.38   | 0.53            | 0.015 | 0.021 |  |  |  |

| F                       | 0.76   | 1.40            | 0.030 | 0.055 |  |  |  |

| G                       | 2.54   | BSC             | 0.100 | BSC   |  |  |  |

| H                       | 0.76   | 1.78            | 0.030 | 0.070 |  |  |  |

| J                       | 0.20   | 0.30            | 0.008 | 0.012 |  |  |  |

| K                       | 2.54   | 4.57            | 0.100 | 0.180 |  |  |  |

| L                       | 14.99  | 15.49           | 0.590 | 0.610 |  |  |  |

| M                       | _      | 10 <sup>0</sup> | - //  | 100   |  |  |  |

| N                       | 1.02   | 1.52            | 0.040 | 0.060 |  |  |  |

| W 1.02 1.52 0.040 0.060 |        |                 |       |       |  |  |  |

L SUFFIX CERAMIC PACKAGE CASE 716-06

| <u>^</u>                                |   |

|-----------------------------------------|---|

| В                                       |   |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |   |

| A                                       | - |

| H- G F D SEATING M                      |   |

| PLANE                                   |   |

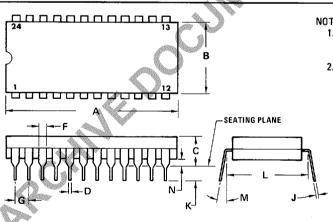

#### NOTES:

- 1. POSITIONAL TOLERANCE OF LEADS (D), SHALL BE WITHIN 0.25 mm (0.010) AT MAXIMUM MATERIAL CONDITION, IN RELATION TO SEATING PLANE AND EACH OTHER.

- 2. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- 3. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

|     | MILLIN | METERS          | INCHES |                 |  |  |  |

|-----|--------|-----------------|--------|-----------------|--|--|--|

| DIM | MIN    | MAX             | MIN    | MAX             |  |  |  |

| Α   | 31.37  | 32.13           | 1.235  | 1.265           |  |  |  |

| В   | 13.72  | 14.22           | 0.540  | 0.560           |  |  |  |

| C   | 3.94   | 5.08            | 0.155  | 0.200           |  |  |  |

| D   | 0.36   | 0.56            | 0.014  | 0.022           |  |  |  |

| F   | 1.02   | 1.52            | 0.040  | 0.060           |  |  |  |

| G   | 2.54   | BSC             | 0.100  | BSC             |  |  |  |

| H   | 1.65   | 2.03            | 0.065  | 0.080           |  |  |  |

| J   | 0.20   | 0.38            | 0.008  | 0.015           |  |  |  |

| K   | 2.92   | 3.43            | 0.115  | 0.135           |  |  |  |

| L   | 15.24  |                 | 0.600  | BSC             |  |  |  |

| M   | Oo     | 15 <sup>0</sup> | Oo     | 15 <sup>0</sup> |  |  |  |

| N   | 0.51   | 1.02            | 0.020  | 0.040           |  |  |  |

## P SUFFIX

PLASTIC PACKAGE CASE 709-02

#### NOTES:

- 1. DIM "L" TO CENTER OF **LEADS WHEN FORMED** PARALLEL.

- 2. LEADS WITHIN 0.13 mm (0.005) RADIUS OF TRUE POSITION AT SEATING PLANE AT MAXIMUM MATERIAL CONDITION. (WHEN FORMED PARALLEL)

|     | MILLIN    | IETERS          | INCHES    |                 |  |

|-----|-----------|-----------------|-----------|-----------------|--|

| DIM | MIN       | MAX             | MIN       | MAX             |  |

| Α   | 31.24     | 32.77           | 1.230     | 1.290           |  |

| В   | 12.70     | 15.49           | 0.500     | 0.610           |  |

| C   | 4.06      | 5.59            | 0.160     | 0.220           |  |

| Đ   | 0.41      | 0.51            | 0.016     | 0.020           |  |

| F   | 1.27      | 1.52            | 0.050     | 0.060           |  |

| G   | 2.54      | BSC             | 0.100 BSC |                 |  |

| J   | 0.20      | 0.30            | 0.008     | 0.012           |  |

| K   | 2.29      | 4.06            | 0.090     | 0.160           |  |

| L   | 15.24 BSC |                 | 0.600 BSC |                 |  |

| M   | 00        | 15 <sup>0</sup> | 00        | 15 <sup>0</sup> |  |

| N   | 0.51      | 1.27            | 0.020     | 0.050           |  |

**S SUFFIX** CERDIP PACKAGE CASE 623-04

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/ Affirmative Action Employer.

## **IOTOROLA** Semiconductor Products Inc.

3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721 ● A SUBSIDIARY OF MOTOROLA INC.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.